添加笔记

This commit is contained in:

165

课设具体内容.md

Normal file

165

课设具体内容.md

Normal file

@@ -0,0 +1,165 @@

|

||||

# 课设具体内容(笔记)

|

||||

|

||||

成绩评定:

|

||||

|

||||

1. 程序运行结果;

|

||||

2. 问问题(包括检查总体结构是否符合数据通路图的基本约定);

|

||||

3. 实验报告。

|

||||

|

||||

要拿A,必须做扩展。

|

||||

|

||||

## 指令

|

||||

|

||||

LD/STA Ri,AD (占用2字节)

|

||||

|

||||

AD表示内存地址,在第二个字节。

|

||||

|

||||

STA 2B

|

||||

|

||||

ADD 1B

|

||||

|

||||

HALT 1B

|

||||

|

||||

## 记忆体储存区

|

||||

|

||||

范例:

|

||||

|

||||

```

|

||||

// 程式码区

|

||||

00H LD

|

||||

01H A1

|

||||

02H LD

|

||||

03H A2

|

||||

04H ADD

|

||||

05H STA

|

||||

06H A3

|

||||

07H HALT

|

||||

|

||||

// 资料区

|

||||

A1 X

|

||||

...

|

||||

A2 Y

|

||||

...

|

||||

A3 00H -> X+Y

|

||||

```

|

||||

|

||||

检查的时候,叫你把A3清零,然后运行程序。运行完之后检查A3里面是不是要的数据。

|

||||

|

||||

## 数据通路

|

||||

|

||||

ALU用的是181、182构成的。

|

||||

|

||||

做扩展时候,可以借用它的功能。

|

||||

|

||||

移位的时候,可以做在暂存器Z里(直传、左移、右移)。

|

||||

|

||||

我们做的结构是以运算器为中心,不做单总线的(19级是单总线的)。所以增加了个MDR部件,起到**隔离**作用(隔离内外总线)。如:

|

||||

|

||||

```

|

||||

M(MAR)->MDR

|

||||

(MDR)->Z

|

||||

(Z)->xxx(指令保存到IR、内存地址保存到MAR等,根据设计的约定)

|

||||

```

|

||||

|

||||

寄存器组的R0保存到记忆体:

|

||||

|

||||

```

|

||||

(R0)->Z

|

||||

(Z)->MDR

|

||||

xxx->MAR

|

||||

M(W)

|

||||

```

|

||||

|

||||

考虑:暂存器Z用移位寄存器,IR、MAR用通用寄存器,PC用计数器(LD:可选加一/置数)。

|

||||

|

||||

差不多总共用6个左右的CP选择信号。

|

||||

|

||||

## 运算结果状态位

|

||||

|

||||

注意溢出判断时要根据算的数据是什么,无符号整数还是补码。补码用最高位判断(即符号位判别法),无符号整数用C判断等。

|

||||

|

||||

可以在保存到暂存器Z的同时,把这一次产生的状态保存到PSW(CVNZ)里。

|

||||

|

||||

## 指令格式

|

||||

|

||||

双倍字长指令:

|

||||

|

||||

| OP | 源寄存器编号 | 目的寄存器编号 |

|

||||

| ---- | ------------ | -------------- |

|

||||

| 4 | 2 | 2 |

|

||||

|

||||

| AD(形式地址,即内存地址) |

|

||||

| -------------------------- |

|

||||

| 8 |

|

||||

|

||||

## 寄存器组

|

||||

|

||||

|

||||

|

||||

四个寄存器。

|

||||

|

||||

一路输入,两路输出。

|

||||

|

||||

**输出:**

|

||||

|

||||

两个输出阀门,每个阀门是八位四选一。四个寄存器,都分别往两个阀门接。

|

||||

|

||||

四选一那么每个阀门有四条选择控制线。

|

||||

|

||||

指令里面有一个源寄存器编号,一个目的寄存器编号,都是两位的。透过一个二四译码器。

|

||||

|

||||

这样可以完成,比如R0+R0->R0。

|

||||

|

||||

**输入:**

|

||||

|

||||

输入的部分来自内总线,外观上看,数据直接连进去。

|

||||

|

||||

统一清零。

|

||||

|

||||

CP进来的时候,透过二四译码器,选一个寄存器打入。

|

||||

|

||||

## 扩展基本要求

|

||||

|

||||

|

||||

|

||||

JX指令:

|

||||

|

||||

偏移量用补码表示。

|

||||

|

||||

当这条指令取完了之后,PC应该是指向下一条指令。

|

||||

|

||||

这个额外的电路是做在CU(控制单元)里,不要做成组合逻辑。

|

||||

|

||||

| OP | ~~源寄存器编号~~测试位(比如,00测试C,01测试V) | |

|

||||

| ---- | ------------------------------------------------ | ---- |

|

||||

| JX | 2 | |

|

||||

|

||||

在ADD那个指令之后,加入一条测试指令,测试True则跳到另一个地方,在这个地方加一条存数指令,存到地址单元里面一个常数。

|

||||

|

||||

不管条件是否成立,这个指令的长度都是两个字节。

|

||||

|

||||

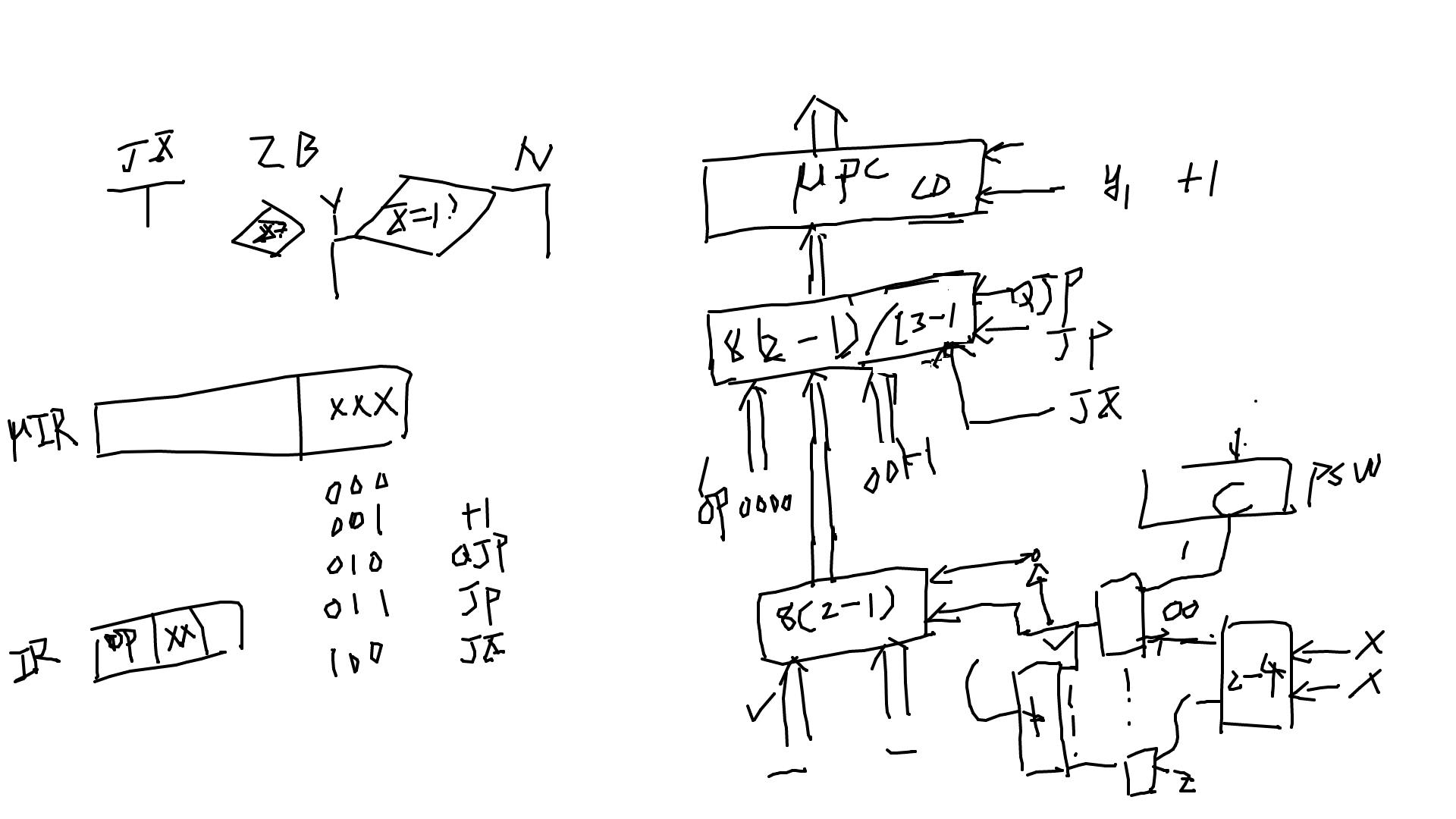

μPC有一个八位二选一,改成三选一。选择条件分别有QJP、JP、JX。

|

||||

|

||||

如果是JX的话,JX对应的数据入口,又是一个八位二选一。需要测试4个东西(CVNZ),作为八位二选一选项的输入。

|

||||

|

||||

为了完成这个要求,还需要加入一条JMP无条件转移指令,转移地址在第二个字节。

|

||||

|

||||

HALT只放在程序最后,不要在程序中多次出现HALT。

|

||||

|

||||

## 扩展进阶要求

|

||||

|

||||

如果用累加的方式,在退出循环的时候用一个东西提示一下是因为溢出而退出循环的还是加完了。

|

||||

|

||||

乘积16位的,要在最高位加上进位的逻辑。

|

||||

|

||||

原码一位乘的思想,即用「加」和「右移」。总共加操作和右移操作都是八次。写一个循环来处理。

|

||||

|

||||

暂存器Z移走的东西不能丢掉,保存到哪?需要增加一些控制点和一些电路。

|

||||

|

||||

实现方式是写一段程序,缺什么指令,自己定义。

|

||||

|

||||

## 事后

|

||||

|

||||

实验报告,可以参考例子,但要增加详细的描述。

|

||||

|

||||

大概会有十几二十几页。

|

||||

Reference in New Issue

Block a user